16-bit ADC/DAC FMC Modules

|

l

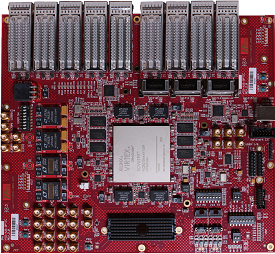

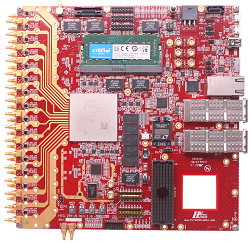

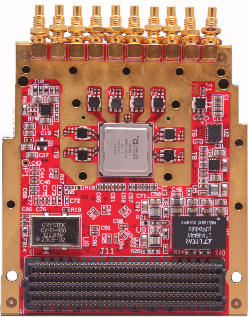

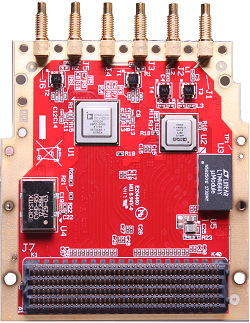

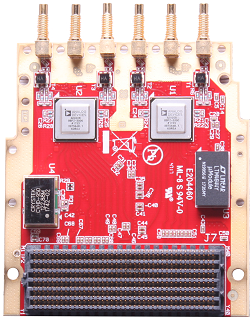

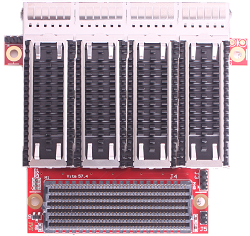

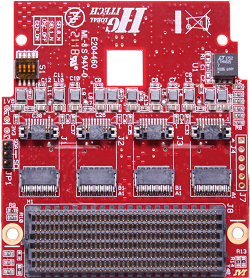

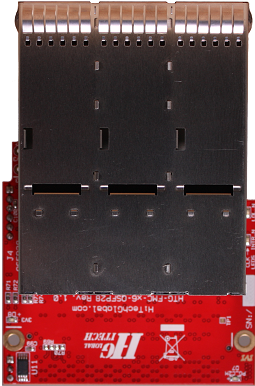

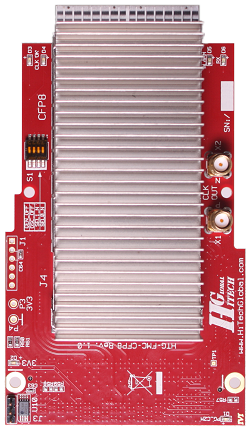

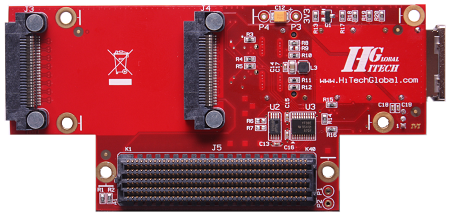

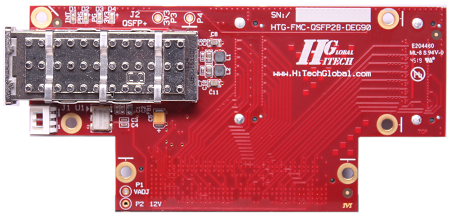

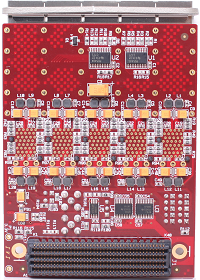

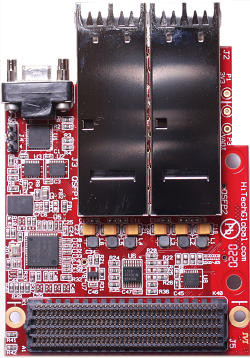

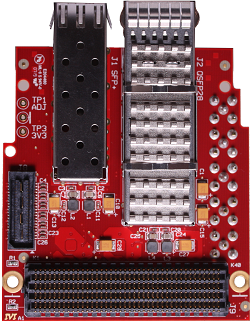

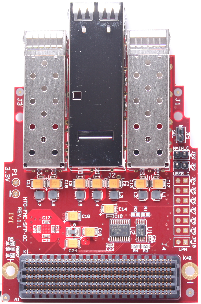

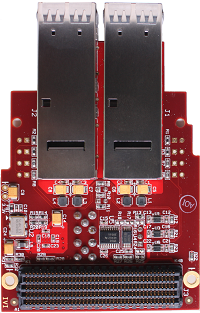

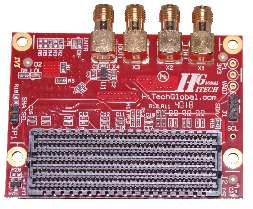

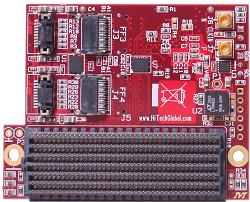

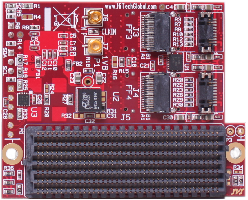

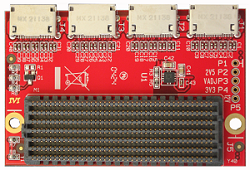

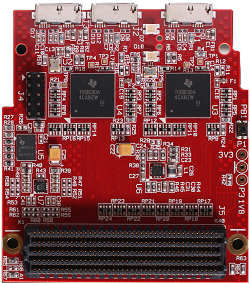

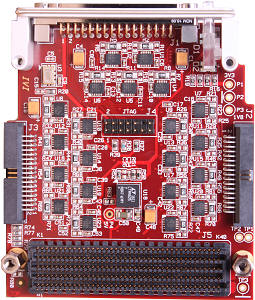

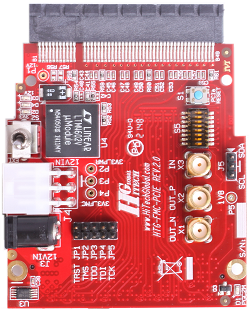

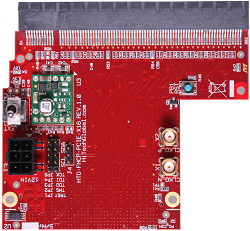

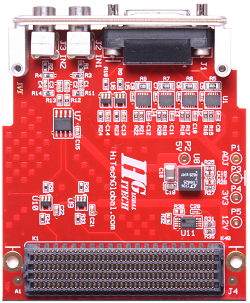

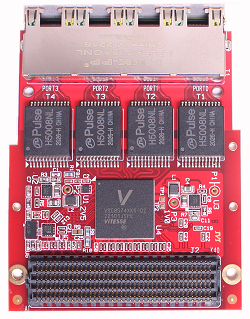

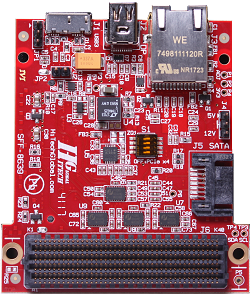

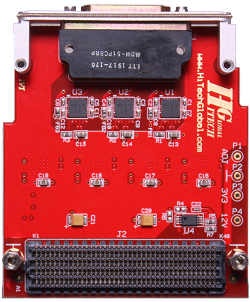

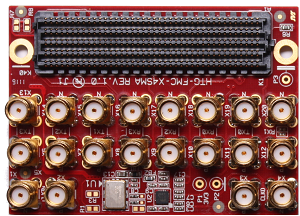

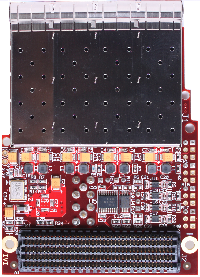

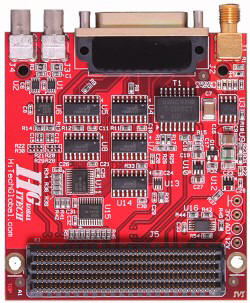

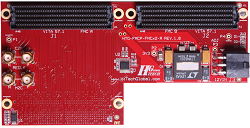

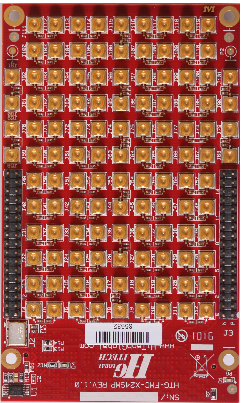

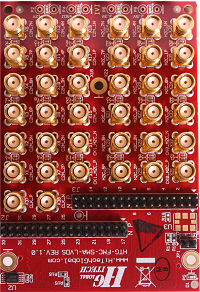

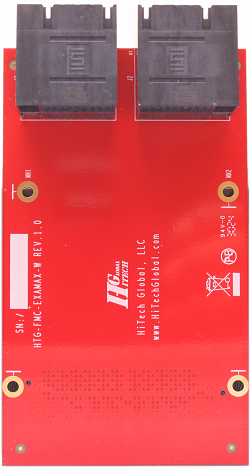

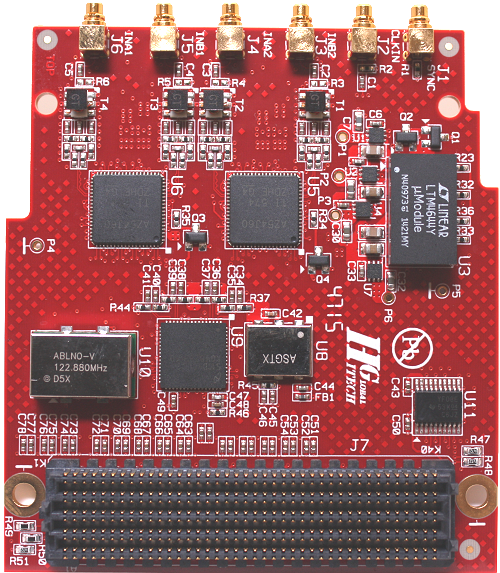

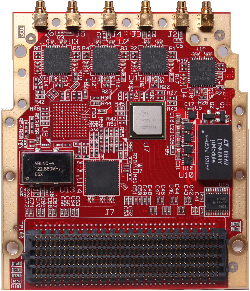

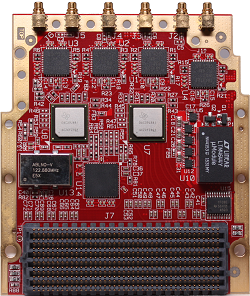

The HTG-ADC16 and HTG-DAC16 modules plug into FMC HPC or HSPC slots in Vita 57.1 or 57.4 compliant FPGA carrier boards and provide access to four 16-bit ADC and two or four DAC channels. The 4-channel DAC (requiring 16 serial transceivers) only works with Vita57.4 compliant FPGA carrier cards such as HTG-9100, HTG-830, or HTG-828 The modules use Texas Instruments ADS54J60 ADC and DAC39J84 DAC devices with JESD204B support. The ADS54J60 is a low-power, wide-bandwidth, 16-bit, 1.0-GSPS, dual-channel, analog-to-digital converter (ADC). Designed for high signal-to-noise ratio (SNR), the device delivers a noise floor of 159 dBFS/Hz for applications aiming for highest dynamic range over a wide instantaneous bandwidth. The device supports the JESD204B serial interface with data rates up to 10.0 Gbps, supporting two or four lanes per ADC. The buffered analog input provides uniform input impedance across a wide frequency range while minimizing sample-and-hold glitch energy. Each ADC channel optionally can be connected to a wideband digital down-converter (DDC) block. The ADS54J60 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption. The JESD204B interface reduces the number of interface lines, allowing high system integration density. An internal phase-locked loop (PLL) multiplies the ADC sampling clock to derive the bit clock that is used to serialize the 16-bit data from each channel. Features

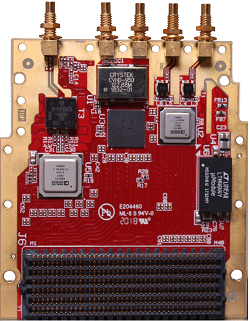

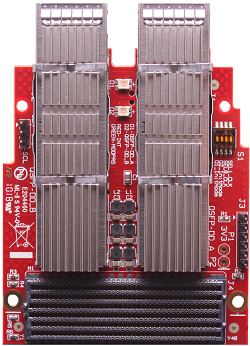

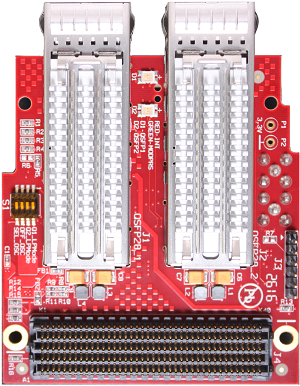

The DAC39J84 is a low power,

16-bit, quad-channel, 2.8 GSPS digital to analog converter (DAC)

with JESD204B interface.Digital data is

input to the device through 1, 2, 4 or 8 configurable serial

JESD204B lanes running up to 12.5 Gbps with on-chip termination

and programmable equalization. The interface allows JESD204B

Subclass 1 SYSREF based deterministic latency and full

synchronization of multiple devices.

The device includes features that simplify the design of complex transmit architectures. Fully bypassable 2x to 16x digital interpolation filters with over 90 dB of stop-band attenuation simplify the data interface and reconstruction filters. An on-chip 48-bit Numerically Controlled Oscillator (NCO) and independent complex mixers allow flexible and accurate carrier placement. A high-performance low jitter PLL simplifies clocking of the device without significant impact on the dynamic range. The digital Quadrature Modulator Correction (QMC) and Group Delay Correction (QDC) enable complete IQ compensation for gain, offset, phase, and group delay between channels in direct up-conversion applications. A programmable Power Amplifier (PA) protection mechanism is available to provide PA protection in cases when the abnormal power behavior of the input data is detected. Features

|

|

Part Number: HTG-FMC-ADS54-4 (4-channel ADC compatible with

Vita57.1 and Vita57.4 carrier boards)

ECCN #:

EAR99

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||